-

产品中心

-

行业应用

-

服务中心

安装手册

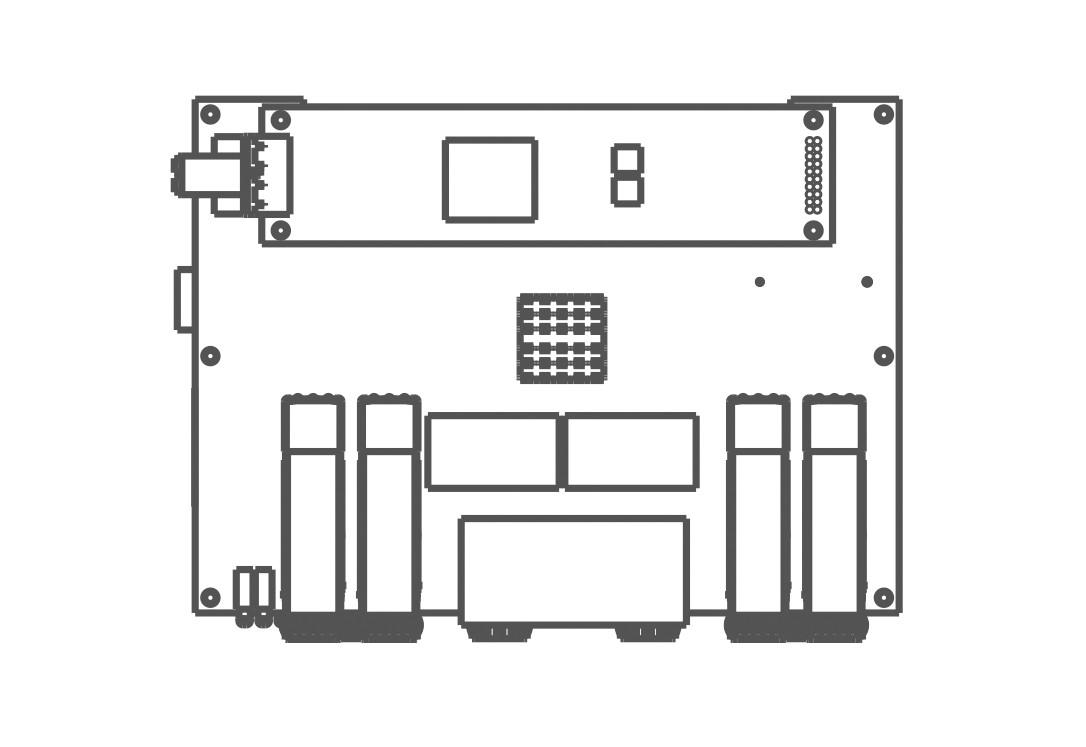

- MES8120G-4GF-16GT 硬件安装手册

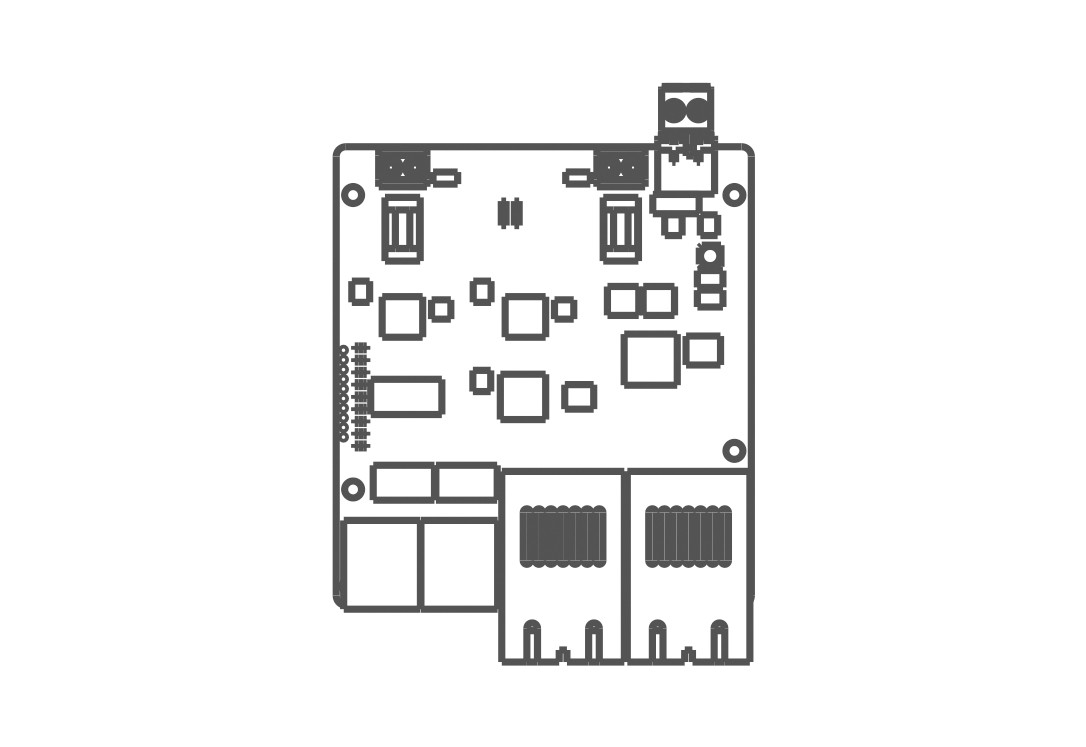

- MGT551 硬件安装手册

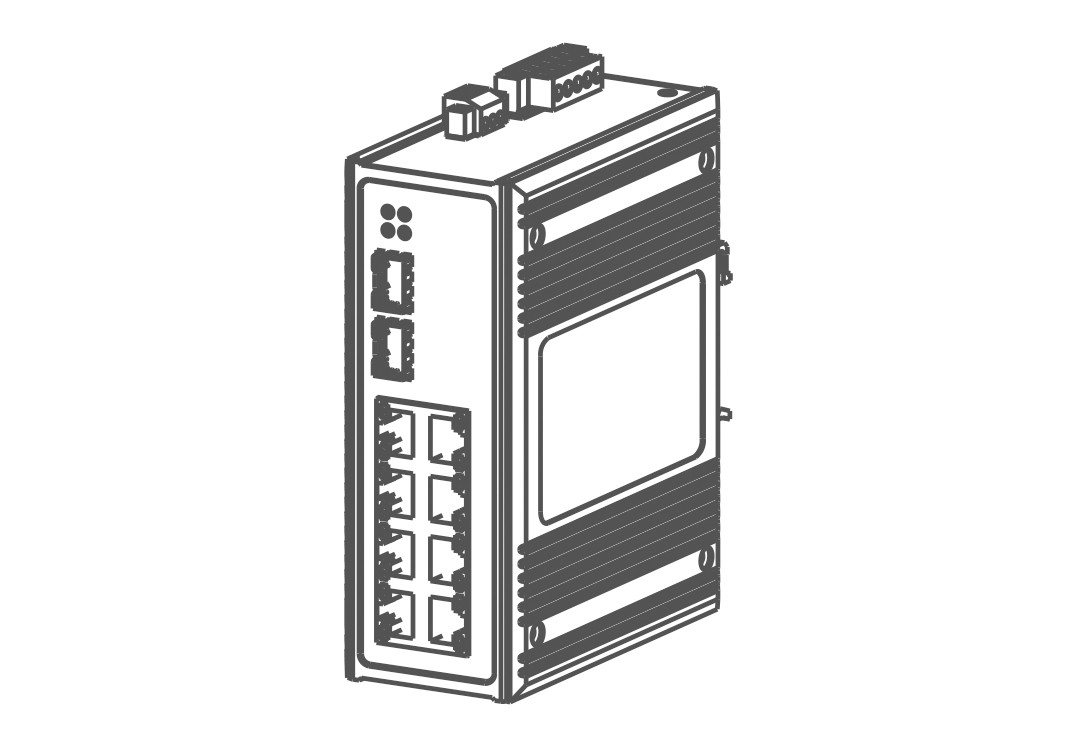

- MISCOM6218-2F 硬件安装手册

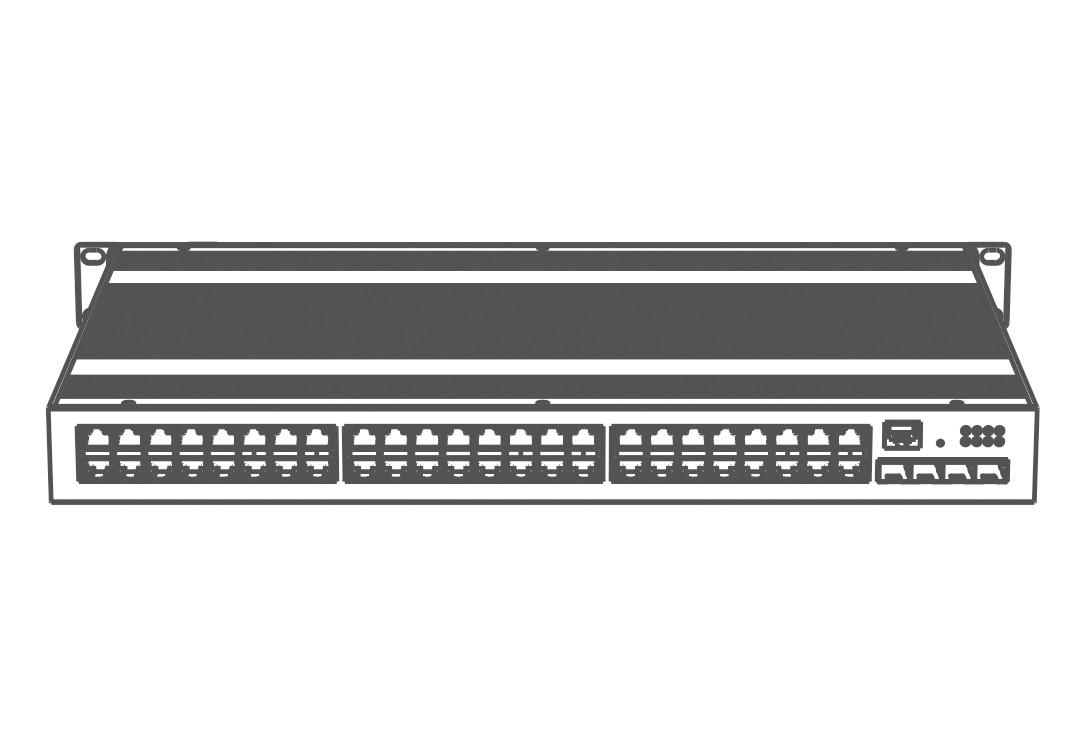

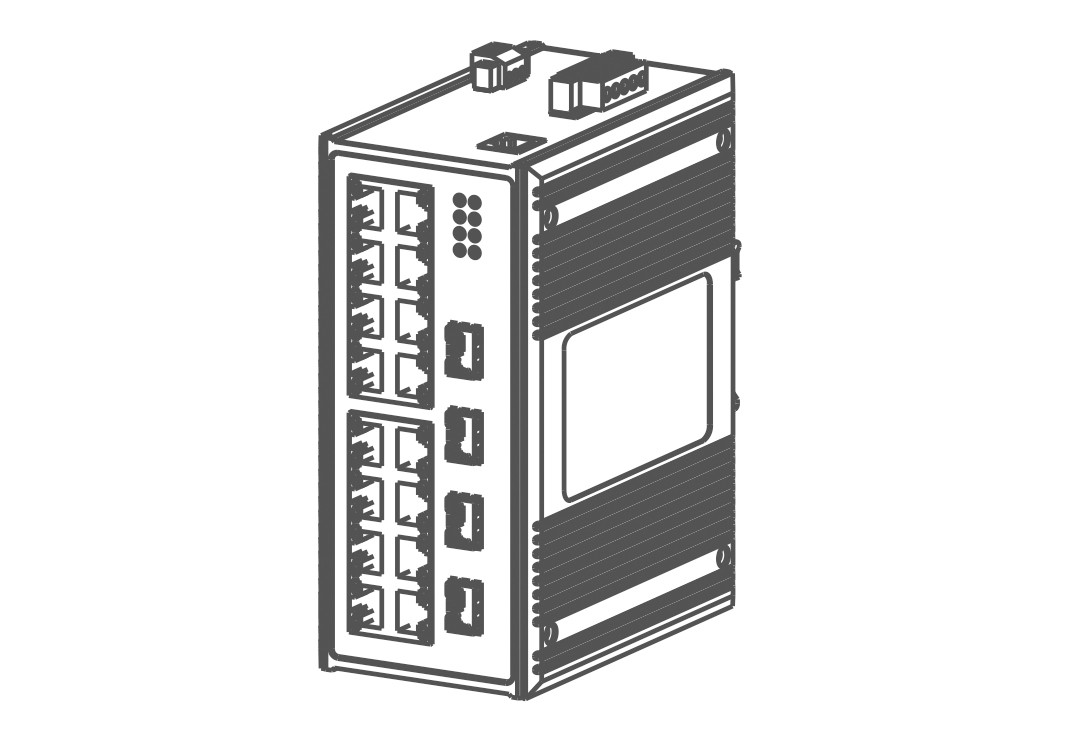

- MISCOM8028GX-4XGF-8GC-16GT 硬件安装手册

- MISCOM8028GX-4XGF-16GF-8GC 硬件安装手册

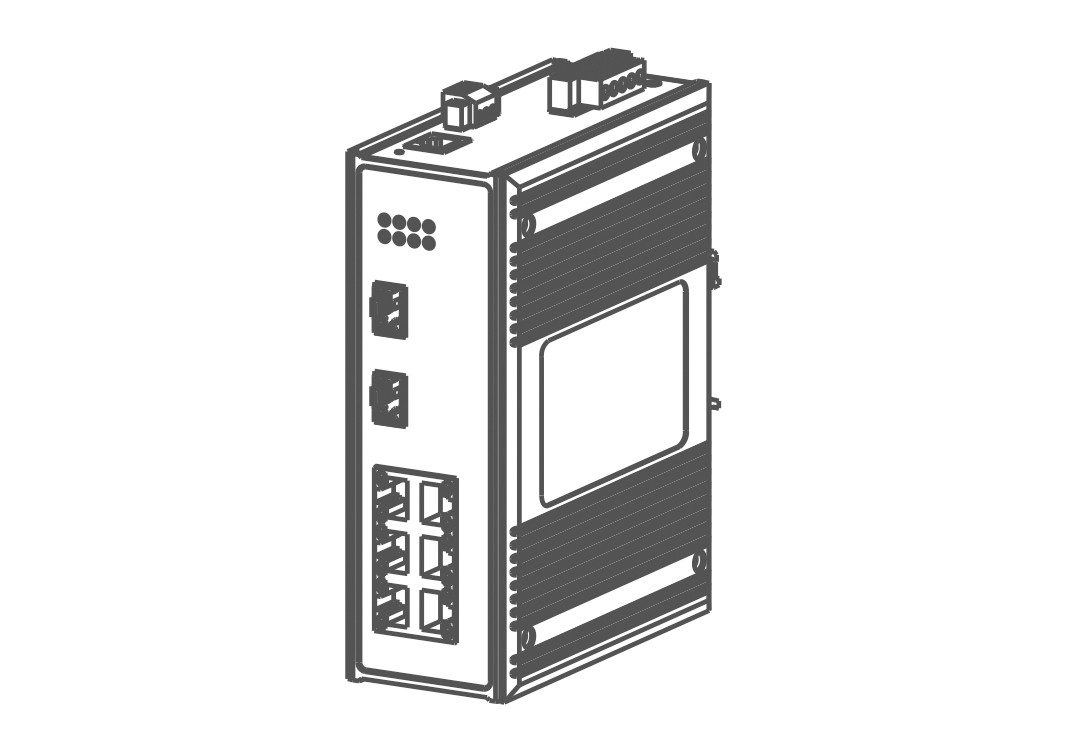

- MISCOM6216 硬件安装手册

用户手册

- MWVirtualCom虚拟串口管理软件 用户手册

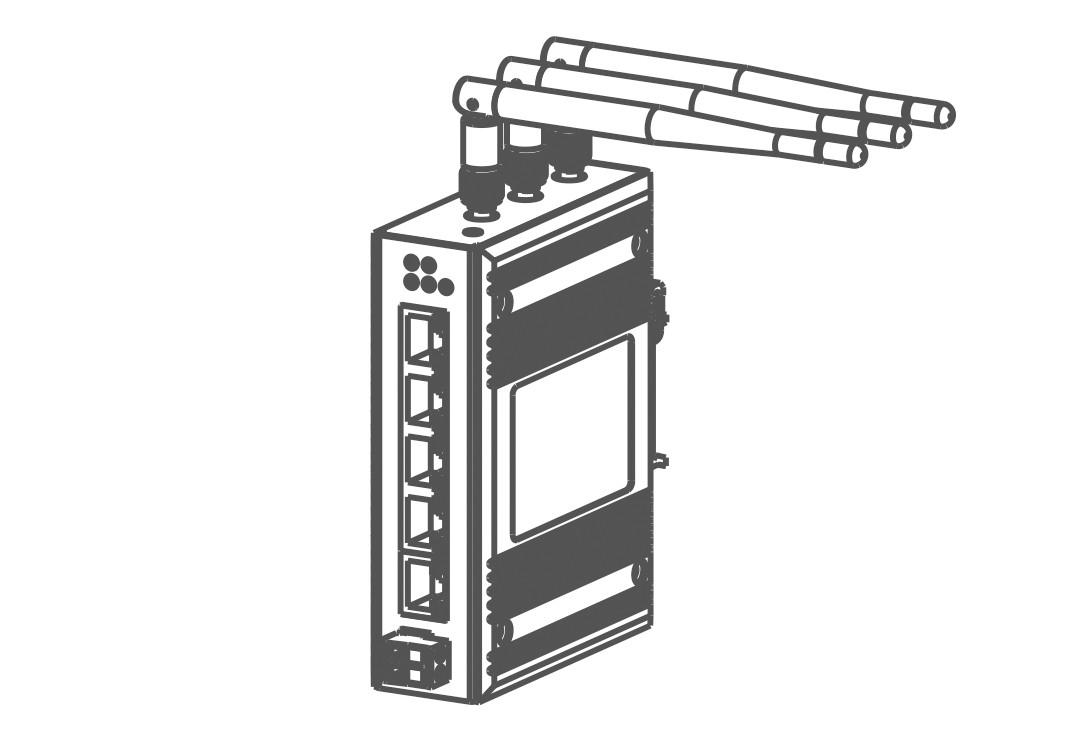

- MIAP6200-2N2-5T 用户手册

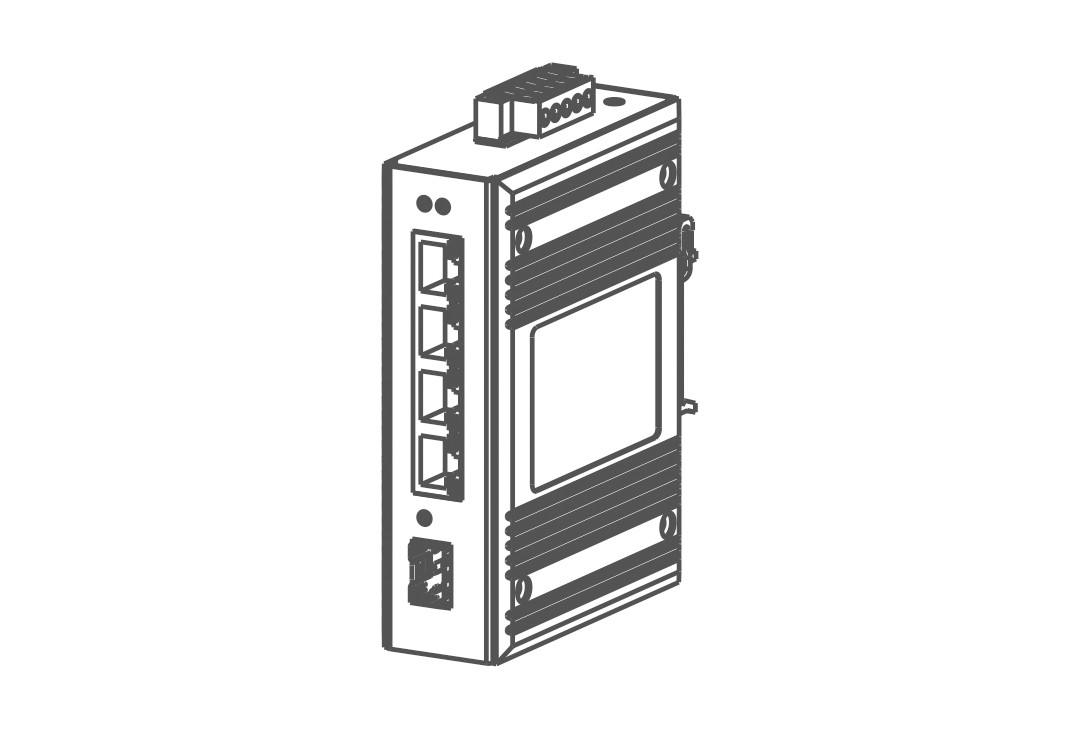

- Mport3101-W 用户手册

- Mport3102 用户手册

- Mport3102-I 用户手册

- Mport3102R 用户手册

产品规格书

- MISCOM6218-2F 规格书

- MISCOM8028GX-4XGF-8GC-16GT 规格书

- MISCOM8028GX-4XGF-16GF-8GC 规格书

- MISCOM6216 规格书

- MIEN5205C系列 规格书

- MISCOM6220-4F 规格书

服务支持

查看更多 我们深知服务的重要性,因此致力于为客户提供全方位的优质服务。我们郑重承诺,所有产品均享有完善的质保政策,确保您购买无忧。在售前,我们的专业团队将为您详细解答疑问,确保您选择到最适合的产品。售后服务方面,我们更是不遗余力,随时为您排忧解难,同时,我们提供RMA服务,让售后问题得到及时解决。我们坚信,只有优质的服务才能赢得客户的信任与支持。选择我们,就是选择品质与保障,我们将竭诚为您服务,共创美好未来。

我们深知服务的重要性,因此致力于为客户提供全方位的优质服务。我们郑重承诺,所有产品均享有完善的质保政策,确保您购买无忧。在售前,我们的专业团队将为您详细解答疑问,确保您选择到最适合的产品。售后服务方面,我们更是不遗余力,随时为您排忧解难,同时,我们提供RMA服务,让售后问题得到及时解决。我们坚信,只有优质的服务才能赢得客户的信任与支持。选择我们,就是选择品质与保障,我们将竭诚为您服务,共创美好未来。常见问题

查看更多 欢迎来到常见问题版块,这里汇集了一些常见的产品问题及解答。无论您是初次接触这些产品,还是在使用过程中遇到了难题,都能在这里找到实用的帮助和指导。通过浏览这些问题与答案,您将能够更深入地了解产品的性能、特点和使用方法,从而更好地满足您的业务需求。我们致力于为您提供最全面、最专业的技术支持,帮助您轻松解决各类问题,实现高效、稳定的工业通信。

欢迎来到常见问题版块,这里汇集了一些常见的产品问题及解答。无论您是初次接触这些产品,还是在使用过程中遇到了难题,都能在这里找到实用的帮助和指导。通过浏览这些问题与答案,您将能够更深入地了解产品的性能、特点和使用方法,从而更好地满足您的业务需求。我们致力于为您提供最全面、最专业的技术支持,帮助您轻松解决各类问题,实现高效、稳定的工业通信。 -

新闻与活动

-

关于迈威

公司简介

查看更多 武汉迈威通信股份有限公司(股票代码:873461)是一家专注于为用户提供可靠的工业互联网通信产品和自主可控的系统解决方案的高新技术企业,总部位于国家级高新技术开发区"武汉·中国光谷",集自主研发、生产、销售、服务于一体,核心业务指标全部进入行业品牌前三名。公司以“成为世界一流的新型工业自动化领导品牌”为企业愿景,旨在让更多的用户能够安全可靠的实现设备联网通信。

武汉迈威通信股份有限公司(股票代码:873461)是一家专注于为用户提供可靠的工业互联网通信产品和自主可控的系统解决方案的高新技术企业,总部位于国家级高新技术开发区"武汉·中国光谷",集自主研发、生产、销售、服务于一体,核心业务指标全部进入行业品牌前三名。公司以“成为世界一流的新型工业自动化领导品牌”为企业愿景,旨在让更多的用户能够安全可靠的实现设备联网通信。加入迈威

查看更多 欢迎加入我们的大家庭!这里是一个汇聚梦想、激发潜能、共创未来的平台。我们秉持开放包容的态度,鼓励创新思维,为每一位成员提供施展才华的广阔舞台。在这里,你将与一群志同道合的伙伴共同奋斗,共同成长。我们期待你的加入能为我们带来新的活力和创意,共同书写属于我们的辉煌篇章。让我们携手并进,共同追求卓越,开创更加美好的未来!

欢迎加入我们的大家庭!这里是一个汇聚梦想、激发潜能、共创未来的平台。我们秉持开放包容的态度,鼓励创新思维,为每一位成员提供施展才华的广阔舞台。在这里,你将与一群志同道合的伙伴共同奋斗,共同成长。我们期待你的加入能为我们带来新的活力和创意,共同书写属于我们的辉煌篇章。让我们携手并进,共同追求卓越,开创更加美好的未来!荣誉资质

查看更多 我们珍视每一份荣誉,因为它们凝结着辛勤的努力与不懈的追求。这些资质,见证了我们的成长与蜕变,也激励着我们不断前行,追求卓越。在未来的道路上,我们将继续秉持诚信、创新、卓越的理念,不断提升自身实力,为社会创造更多价值。让我们以荣誉为引,携手共进,书写更加辉煌的篇章!

我们珍视每一份荣誉,因为它们凝结着辛勤的努力与不懈的追求。这些资质,见证了我们的成长与蜕变,也激励着我们不断前行,追求卓越。在未来的道路上,我们将继续秉持诚信、创新、卓越的理念,不断提升自身实力,为社会创造更多价值。让我们以荣誉为引,携手共进,书写更加辉煌的篇章!发展历程

查看更多 自创立之初,我们秉持着坚定的信念与不懈的追求,一路砥砺前行。历经风雨洗礼,我们不断成长壮大,汇聚起无数智慧与力量,共同书写着属于我们的辉煌篇章。如今,我们站在新的历史起点上,回望过去,我们为取得的成就感到自豪;展望未来,我们满怀信心,期待着更加美好的明天。我们将继续秉承初心,坚守使命,以更加昂扬的斗志和更加务实的作风,开创更加辉煌的未来,为梦想的实现而努力奋斗。

自创立之初,我们秉持着坚定的信念与不懈的追求,一路砥砺前行。历经风雨洗礼,我们不断成长壮大,汇聚起无数智慧与力量,共同书写着属于我们的辉煌篇章。如今,我们站在新的历史起点上,回望过去,我们为取得的成就感到自豪;展望未来,我们满怀信心,期待着更加美好的明天。我们将继续秉承初心,坚守使命,以更加昂扬的斗志和更加务实的作风,开创更加辉煌的未来,为梦想的实现而努力奋斗。联系我们

查看更多 欢迎您与我们取得联系!我们始终秉持着开放、友好的态度,期待与您建立长期稳定的合作关系。无论您有任何疑问、需求或建议,都请随时与我们沟通。我们承诺会尽快回复您的每一条信息,提供满意的答复与专业的解决方案。我们深信,每一次的交流与合作,都将成为我们共同进步的阶梯。请放心,您的信任与支持,将是我们不断前行的动力。期待您的来信,让我们携手共创美好未来!

欢迎您与我们取得联系!我们始终秉持着开放、友好的态度,期待与您建立长期稳定的合作关系。无论您有任何疑问、需求或建议,都请随时与我们沟通。我们承诺会尽快回复您的每一条信息,提供满意的答复与专业的解决方案。我们深信,每一次的交流与合作,都将成为我们共同进步的阶梯。请放心,您的信任与支持,将是我们不断前行的动力。期待您的来信,让我们携手共创美好未来!

-

- Q:X86架构与ARM架构的区别

-

这就是“复杂指令集”和“精简指令集”的逻辑区别。可能有人说,明显是精简指令集好啊,但是我们不好去判断它们之间到底谁好谁坏,因为目前他们两种指令集都在蓬勃发展,而且都很成功——X86是复杂指令集(CISC)的代表,而ARM则是精简指令集(RISC)的代表,甚至ARM的名字就直接表明了它的技术:Advanced RISC Machine——高级RISC机。

到了这里你就应该明白为什么RISC和CISC之间不好直接比较性能了,因为它们之间的设计思路差异太大。这样的思路导致了CISC和RISC分道扬镳——前者更加专注于高性能但同时高功耗的实现,而后者则专注于小尺寸低功耗领域。实际上也有很多事情CISC更加合适,而另外一些事情则是RISC更加合适,比如在执行高密度的运算任务的时候CISC就更具备优势,而在执行简单重复劳动的时候RISC就能占到上风,比如假设我们是在举办吃饭大赛,那么CISC只需要不停的喊“吃饭吃饭吃饭”就行了,而RISC则要一遍一遍重复吃饭流程,负责喊话的人如果嘴巴不够快(即内存带宽不够大),那么RISC就很难吃的过CISC。但是如果我们只是要两个人把饭舀出来,那么CISC就麻烦得多,因为CISC里没有这么简单的舀饭动作,而RISC就只需要不停喊“舀饭舀饭舀饭”就OK。

这就是CISC和RISC之间的区别。但是在实际情况中问题要比这复杂许许多多,因为各个阵营的设计者都想要提升自家架构的性能。这里面最普遍的就是所谓的“发射”概念。什么叫发射?发射就是同时可以执行多少指令的意思,例如双发射就意味着CPU可以同时拾取两条指令,三发射则自然就是三条了。现代高级处理器已经很少有单发射的实现,例如Cortex A8和A9都是双发射的RISC,而Cortex A15则是三发射。ATOM是双发射CISC,Core系列甚至做到了四发射——这个方面大家倒是不相上下,但是不要忘了CISC的指令更加复杂,也就意味着指令更加强大,还是吃饭的例子,CISC只需要1个指令,而RISC需要5个,那么在内存带宽相同的情况下,CISC能达到的性能是要超过RISC的(就吃饭而言是5倍),而实际中CISC的Core i处理器内存带宽已经超过了100GB/s,而ARM还在为10GB/s而苦苦奋斗,一个更加吃带宽的架构,带宽却只有别人的十分之一,性能自然会受到非常大的制约。为什么说ARM和X86不好比,这也是很重要的一个原因,因为不同的应用对带宽需求是不同的。一旦遇到带宽瓶颈,哪怕ARM处理器已经达到了很高的运算性能,实际上根本发挥不出来,自然也就会落败了。

收起

-

- Q:所谓的“嵌入式安装”是什么意思?

-

嵌入式安装指的是不需要螺丝但通过卡簧或其他卡式回弹片直接卡到产品开孔位置。

收起

-

- Q:嵌入式应用通常需要考虑低功耗设计,即俗称的“省电”,这是因为?

-

这是由嵌入式系统的功耗约束特点决定的

收起

-

- Q:为什么低功耗为嵌入式系统研发关键

-

即使是在诸如物联网应用的无线连接这种主导功耗的事件中,让尽可能多的进程自主运行,也可大大提高电池寿命。降低功耗一直是微控器(MCU)市场的一个主要关注点。超低功耗MCU现在可以大大降低工作模式和深度睡眠模式下的功耗。这种变化的效果是显而易见的,它大大提高了我们日常嵌入式应用中的电池寿命,并且提供了在未来使用能量收集的可能性。

然而,要基于新型MCU降低功耗,开发人员必须考虑到许多因素,对此Silicon Labs特别撰写一篇技术文章:“以0 MIPS运行你的嵌入式系统”,帮助开发人员了解如何利用新型MCU中外设的自主运行,通过更接近以“0”MIPS运行,来实现数据手册中所承诺的低功耗。

对于在功耗敏感型物联网(IoT)应用中所使用的新型MCU和无线MCU(WMCU)来说,执行代码时的功耗已经明显下降,甚至达到40μA/ MHz以下。使用这些低功耗规格,您可能会想知道为什么我们需要睡眠模式,为什么不以500 kHz运行您的代码来实现20μA的电流消耗,并且允许您的应用使用电池运行10年?其实事情并不是这么简单的。

睡眠模式下的功耗在过去几年中也有显著的改善。我们现在可以看到深度睡眠模式下的功耗低于2μA,而一些睡眠模式下的功耗甚至低于50 nA。您可能会觉得拥有这些模式设计出来的系统功耗自然很低,然而事实并非如此,应用能否利用睡眠模式才是关键。

收起

顶部

京东商城

京东商城 天猫商城

天猫商城